Energy and Performance Optimized Infrastructure for Complex Chips for the AI Era

Digital

Digital

Digital

Digital

Digital

Digital

Digital

Digital

Digital

Digital

Featured In

“Movellus Recognized by Frost & Sullivan for Improving System Performance and Optimizing Power with Its Aeonic™ IP Portfolio”

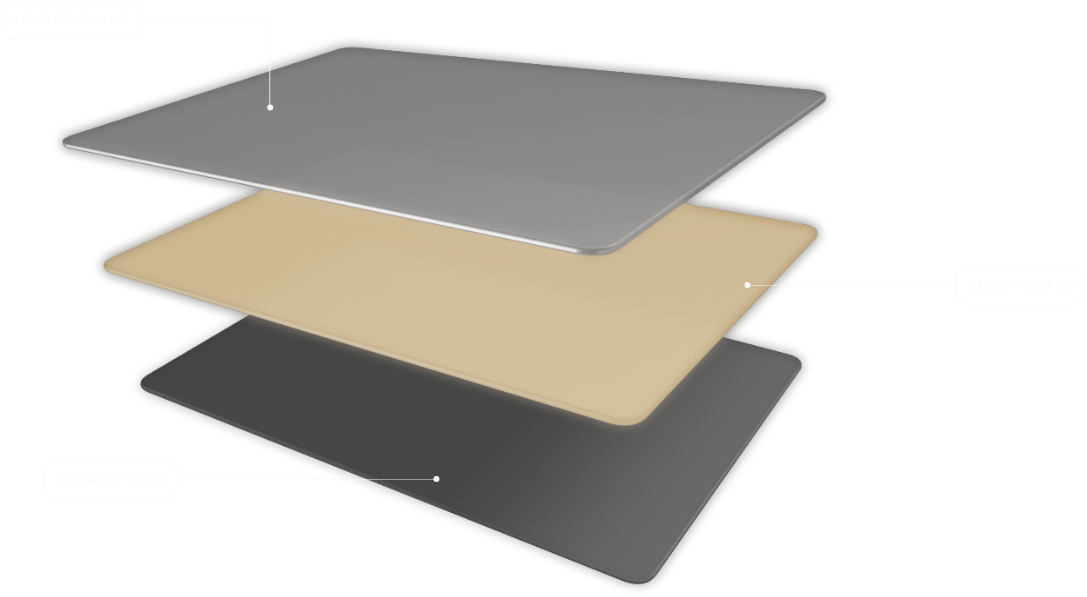

Critical Infrastructure for the AI Era

All chips consist of logical elements interconnected with layers of infrastructure. Movellus delivers infrastructure IP to optimize power, performance and reliability

SENSOR PLANE

Aeonic Insight™

Aeonic Insight™ delivers cutting-edge on-die telemetry for actionable insights. It features advanced sensors with telemetry capabilities, offering design teams unprecedented visibility into power grids, clock health, and more that can be seamlessly integrated with third-party silicon analytic platforms, enhancing data-driven design decision making.

01

CLOCK PLANE

Aeonic Generate™

The Aeonic Generate family features synthesizable, area-efficient clock generation solutions with a high degree of observability. They enable fine-grained droop/DVFS response and architectural innovation through novel strategies like per-core distributed clocking.

02

POWER PLANE

Aeonic Power™

The Aeonic Power™ product family revolutionizes SoC power delivery with integrated on-die voltage regulation, enabling energy and BOM optimization. The highly configurable architecture is designed to address a range of requirements, and offers sophisticated PDN-oriented telemetry, providing unparalleled insights into the power behavior of SoCs and chiplets.

03

Market

Segments

Datacenter

IP solutions to optimize system performance and power for compute, networking, and AI applications.

Mobile

Energy optimization IP that maximizes battery life for the next generation of compute-intensive, heterogeneous mobile SoCs.

Automotive

High reliability IP that enables energy efficient ADAS and digital cockpit applications.

Mil/Aero

Silicon proven rad-hard-ready IP that maximizes reliability for mission critical applications.

Edge AI

Energy and performance optimized IP that enables the next generation of multimodal edge AI solutions.